1st semester Practical Syllabus for MSc Electronics & Telecommunication under Gauhati University

|

A) Analog & Digital Design and Microprocessor

(50 marks)

|

||

|

1

|

Verification of voltage division and current

division rule by using DC networks.

|

|

|

2

|

Design

and study of half wave rectifier with and without filter network.

|

|

|

3

|

Design

and study of centre tapped full wave rectifier with and without filter

network.

|

|

|

4

|

Design

and study of full wave bridge rectifier with and without filter network.

|

|

|

5

|

Design and study of DC voltage regulator circuit

by using zener diode.

|

|

|

6

|

Design

and study of DC voltage regulator by using Zener diode and BJT.

|

|

|

7

|

Design and study

of first order passive and active low pass RC filter circuits

|

|

|

8

|

Design and study

of first order passive and active high pass RC filter circuits

|

|

|

9

|

Design and study

of first order passive and active band pass RC filter circuits

|

|

|

10

|

Design and study

of first order passive and active band elimination RC filter circuits

|

|

|

11

|

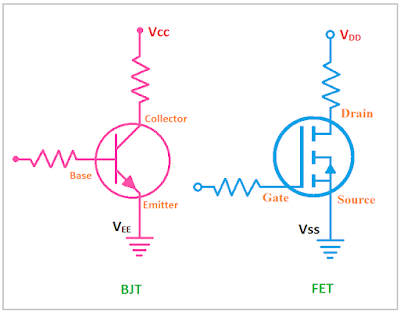

Design and study

of BJT/JFET DC biasing networks by using different biasing schemes

|

|

|

12

|

Design and study

of single stage RC coupled BJT/JFET amplifier circuit

|

|

|

13

|

Design and study

of voltage follower circuit by using BJT

|

|

|

14

|

Design and study

of analog adder and subtraction circuits by using operational amplifiers

|

|

|

15

|

Design and study

of inverting amplifier circuit by

using operational amplifier

|

|

|

16

|

Design and study

of non- inverting amplifiers circuit

by using operational amplifier

|

|

|

17

|

Design of

comparator circuits by using operational amplifier

|

|

|

18

|

Design and study

of astable multivibrator by using BJTs /555 Timer

|

|

|

19

|

Design and study

of monostable multivibrator by using BJTs /555 Timer |

|

|

20

|

Design and study

of basic AND, OR, NOT, NAND logic gates by using diode, transistors.

|

|

|

21

|

Verification of

truth tables for basic logic gates by using logic gate ICs.

|

|

|

22

|

Design and

implementation of half adder and full

adder circuit by using basic logic gates

|

|

|

23

|

Design and

implementation of 4:1 multiplexer circuit by using logic gates

|

|

|

24

|

Design and study

of single bit magnitude comparator circuit by using logic gates

|

|

|

B)

Microprocessor-I (50 marks)

|

||

|

1

|

ALP to move a block of data in

memory location starting from XXXX to a location YYYY. Perform the block move

in reverse order as well

|

|

|

2

|

ALP to find sum of 10 data

bytes stored in consecutive memory locations

|

|

|

3

|

ALP to find largest of 10 data

bytes stored in consecutive memory locations

|

|

|

4

|

ALP to find smallest of 10 data

bytes stored in consecutive memory locations

|

|

|

5

|

ALP to find sum of two 16 bit data stored in four consecutive

memory locations

|

|

|

6

|

ALP to convert binary number to

decimal and decimal to binary

|

|

|

7

|

ALP to convert decimal to

binary and binary to ASCII codes

|

|

|

8

|

ALP to find sum, difference and

product of two 8bit data

|

|

|

9

|

ALP to generate a square wave

through 8255 Ports

|

|

|

10

|

ALP to glow an LED on receiving

an interrupt signal

|

|

|

12

|

ALP to display decimal number

on seven segment display

|

|

|

13

|

ALP to control DC motor /

stepper motor speed through pulse width modulation

|

|

|

13

|

ALP to rotate a DC motor in

clockwise and anti clockwise directions

|

|